# On the Performance of Low-Noise Low-DC-Power-Consumption Cryogenic Amplifiers

I. Angelov, *Member, IEEE*, N. Wadefalk, Jörgen Stenarson, *Student Member, IEEE*, Erik Ludvig Kollberg, *Fellow, IEEE*, Piotr Starski, *Senior Member, IEEE*, and Herbert Zirath, *Member, IEEE*

**Abstract**—The performance of broad-band low-noise low-dc-power-consumption cryogenic amplifiers have been studied in detail with emphasis on minimizing the power consumption and optimizing the amplifier performance at cryogenic temperature. A general approach is presented for the modeling and amplifier design, which helps in minimizing the power consumption and optimizing the performance of the amplifier. A noise temperature below 9 K and 22-dB gain was experimentally obtained in the frequency range of 4–8 GHz with a total power consumption of 4 mW with commercial GaAs transistors.

**Index Terms**—Empirical large-signal models, FET, FET noise models, modeling, noise model extraction, noise parameter.

## I. INTRODUCTION

InP TRANSISTOR devices are known for their very good noise performance and low dc power consumption [1]–[5]. In recent years, the performance of microwave GaAs and InP transistors has improved significantly and many successful designs with high performance have been reported [1]–[5]. GaAs devices have also obtained improved performance and especially the metamorphic InAlAsGaAs on GaAs substrate have improved very much [6].

This, together with the existence of simple and accurate models [7]–[13], has improved the quality of microwave cryogenic amplifiers and excellent results have been achieved in recent years. For many different applications, such as deep space communication, a low-dc-power dissipation can be a crucial requirement for the system.

## II. DEVICE MODELING

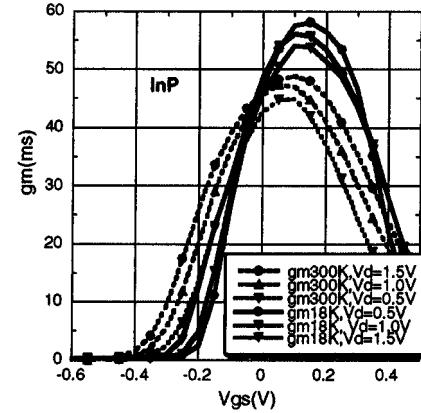

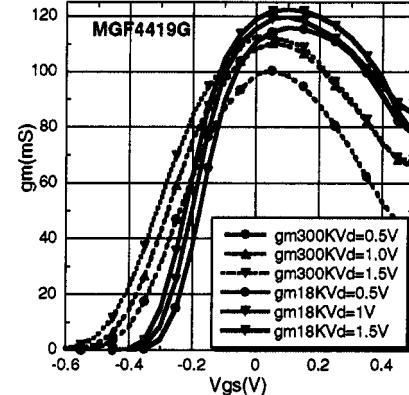

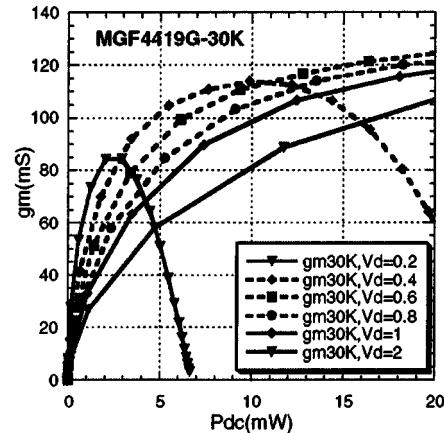

From on-wafer measurements of dc *S*-parameter and noise measurements both at room and cryogenic temperatures, noise models parameters [7]–[14] were extracted and subsequently used for the amplifier design. The transconductance of both InP and GaAs transistors increases at low temperatures (Figs. 1 and 2). Thus, a very high transconductance can be obtained at low drain voltages and low dissipated power (Fig. 3). As can be seen

Manuscript received October 20, 2000; revised October 5, 2001. This work was supported by the Swedish Space Corporation.

I. Angelov, N. Wadefalk, J. Stenarson, E. L. Kollberg, and P. Starski are with the Department of Microwave Technology, Chalmers University of Technology, S-41296 Göteborg, Sweden.

H. Zirath with the Department of Microwave Technology, Chalmers University of Technology, S-41296 Göteborg, Sweden and also with Microwave System AB, Ericsson, S-4384 Mölndal, Sweden.

Publisher Item Identifier S 0018-9480(02)05210-9.

Fig. 1.  $g_m$  versus  $P_{dc}$  for InP transistor.

Fig. 2.  $g_m$  versus  $P_{dc}$  for GaAs FET MGF4419G.

Fig. 3.  $g_m$  versus  $P_{dc}$  for GaAs FET MGF4419G.

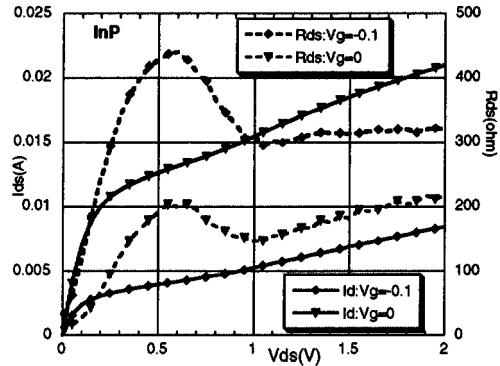

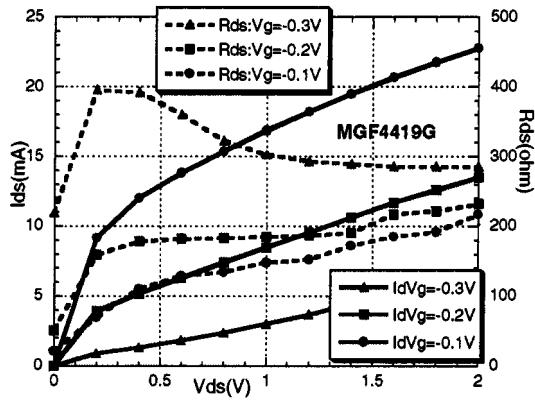

Fig. 4.  $I_{dS}$ ,  $R_{dS}$  for InP transistor.Fig. 5.  $I_{dS}$ ,  $R_{dS}$  for MGF4419G.

in Fig. 3, high transconductance can be reached with 2–3-mW dissipated dc power and a drain voltage below  $V_{ds} = 0.8$  V.

At very low drain voltages,  $V_{ds} < 0.3$ –0.4 V, the output conductance is rather high and this can produce a significant reduction of transistor gain (Figs. 4 and 5). Also, at very low  $V_{ds}$ , almost all other transistor parameters, i.e.,  $C_{gs}$ ,  $C_{gd}$ ,  $g_m$ ,  $f_t$ , . . . , vary significantly.

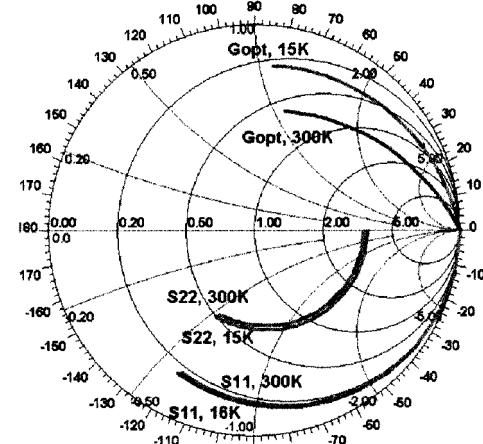

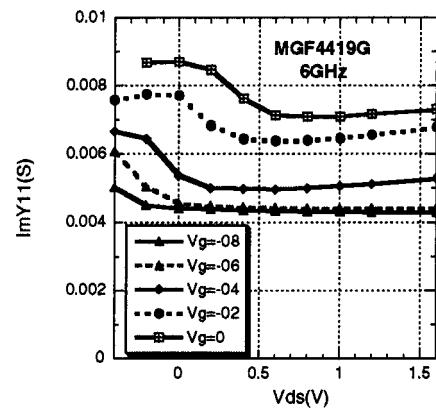

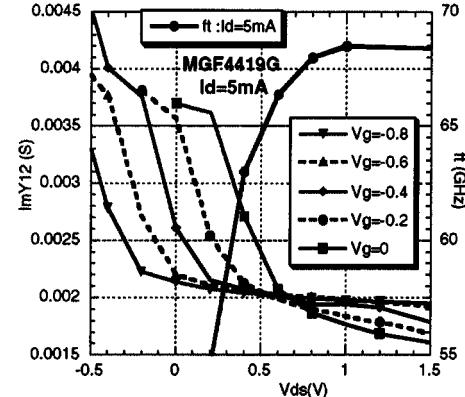

Fig. 6 shows the measured  $S_{11}$ ,  $S_{22}$ , and  $\Gamma_{opt}$  for GaAs transistor MGF4419G (Mitsubishi). From the imaginary part of  $Y_{11}$  and  $Y_{12}$  (Figs. 7 and 8), it can be seen that the capacitive part of the transistor changes significantly at drain voltages  $V_{ds}$  below 0.4 V.

This situation is similar for InP high electron mobility transistors (HEMTs) and can create problems in the design of broad-band amplifiers because of the large change upon bias ( $V_{ds}$ ) of the transistor parameters  $Y_{11}$ ,  $Y_{12}$ ,  $g_m$ ,  $f_t$  and the respective sensitivity of amplifier performance.

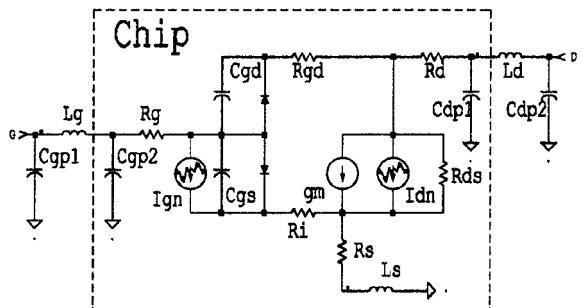

Fig. 9 shows the equivalent circuit of the transistor and the main parameters are listed in Tables I–III. The transconductance  $g_m$ ,  $C_{gs}$ ,  $C_{gd}$ , and  $R_{ds}$  depend strongly on  $V_{ds}$  and the conventional simplified (1) for  $f_t$  will predict  $f_t$  with significant error. We have found (2) to be more accurate [15] as follows:

$$f_t = \frac{g_m}{2\pi(C_{gs} + C_{gd})} \quad (1)$$

$$f_t = \frac{g_m}{2\pi[C_{gs} + C_{gd}]} \cdot \frac{1}{[1 + (R_s + R_d)/R_{ds}] + C_{gd} \cdot g_m \cdot (R_s + R_d)} \quad (2)$$

Fig. 6.  $S_{11}$  and  $G_{opt}$  at 15 and 300 K for MGF4419G.Fig. 7.  $\text{Im}(Y_{11})$  for MGF4419G,  $f = 6$  GHz,  $I_{ds} = 5$  mA.Fig. 8.  $\text{Im}(Y_{12})$ ,  $f_t$  for MGF4419G,  $f = 6$  GHz,  $I_{ds} = 5$  mA.

Fig. 9. Equivalent circuit of the transistor.

TABLE I

MGF4419G, 8 GHz

| V <sub>ds</sub> =0.4<br>Id=10mA | <i>g<sub>m</sub></i><br>mS | <i>g<sub>d</sub></i><br>mS | T <sub>m</sub><br>K | Z <sub>opt</sub><br>Ω | R <sub>n</sub><br>Ω | T <sub>d</sub><br>K | R <sub>t</sub><br>Ω |

|---------------------------------|----------------------------|----------------------------|---------------------|-----------------------|---------------------|---------------------|---------------------|

| T=300K                          | 89.4                       | 12                         | 35                  | 50+j101               | 15.2                | 2100                | 2                   |

| T=15K<br>Id=5mA                 | 83.6                       | 9                          | 4.5                 | 20+j100               | 3.85                | 870                 | 1.9                 |

| V <sub>ds</sub> =1V<br>Id=10mA  | <i>g<sub>m</sub></i><br>mS | <i>g<sub>d</sub></i><br>mS | T <sub>m</sub><br>K | Z <sub>opt</sub><br>Ω | R <sub>n</sub><br>Ω | T <sub>d</sub><br>K | R <sub>t</sub><br>Ω |

| T=300K                          | 89.0                       | 7.4                        | 30                  | 57+j105               | 12.8                | 2750                | 1.8                 |

| T=15K<br>Id=5mA                 | 85.8                       | 6.4                        | 3.7                 | 23+j104               | 3.1                 | 1000                | 1.8                 |

TABLE II

| I <sub>pk0</sub> | P <sub>1</sub>  | P <sub>2</sub>  | P <sub>3</sub>  | V <sub>pks</sub> | DV <sub>ps</sub> | α <sub>r</sub>  | α <sub>s</sub>  | λ               | B <sub>1</sub>  | B <sub>2</sub>   |

|------------------|-----------------|-----------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|

| 56               | 2.2             | -0.3            | 2.2             | 0.15             | 0.25             | 0.1             | 2.5             | 0.22            | 0.7             | 3.2              |

| C <sub>gs0</sub> | P <sub>10</sub> | P <sub>11</sub> | P <sub>20</sub> | P <sub>21</sub>  | C <sub>gd0</sub> | P <sub>30</sub> | P <sub>31</sub> | P <sub>40</sub> | P <sub>41</sub> | C <sub>gd0</sub> |

| 42               | 0               | 1.8             | 0               | 0.3              | 42               | 0               | 0.3             | 0               | 1.8             | 15               |

TABLE III

| t <sub>m</sub> | K <sub>nd1</sub> | K <sub>nd2</sub> | K <sub>np1</sub> |

|----------------|------------------|------------------|------------------|

| 5              | 15.1             | 0.4              | 120              |

where

$$g_m = I_{pk} P_1 \cdot \operatorname{sech}^2(P_1 V_{gs}) \tanh(\alpha V_{ds}) (1 + \lambda V_{ds}) \quad (3)$$

$$g_{ds} = I_{pk} (1 + \tanh(\psi)) (\alpha(1 + \lambda V_{ds}) \operatorname{sech}^2(\alpha \cdot V_{ds})^2 + \lambda \tanh(\alpha V_{ds})) \quad (4)$$

$$C_{gs} = C_{gsp} + C_{gs0} (1 + \tanh[P_{10} + P_{11} \cdot V_{gs}]) \cdot (1 + \tanh[P_{20} + P_{21} \cdot V_{ds}]) \quad (5)$$

$$C_{gd} = C_{gd0} + C_{gd0} (1 + \tanh[P_{30} - P_{31} \cdot V_{ds}]) \cdot (1 + \tanh[P_{40} + P_{41} \cdot V_{gd}]) \quad (6)$$

$$I_{ds} = I_{pko} \cdot (1 + \tanh(\psi)) \tanh(\alpha V_{ds}) (1 + \lambda V_{ds}). \quad (7)$$

For details concerning this model, see [21] and [22]. As the drain voltage increases above  $V_{ds} > 0.5$  V, the total gate capacitance is nearly constant ( $Y_{11}$ ) (Fig. 7),  $Y_{12}$  ( $C_{gd}$ ) does not change significantly (Fig. 8), and the intrinsic  $f_t$  follows the  $g_m$  dependence and is reaching a maximum at a drain voltage approximately equal to the knee voltage (where the drain voltage is just sufficient to saturate the carrier velocity). In order to simultaneously optimize the noise performance and minimize the dc power consumption, the noise models computed from the large-signal model can be used. This can also help to optimize device size for the desired frequency of operation because all parameters needed to calculate the noise parameters and dissipated power are available from the noise and large-signal transistor models [7]–[14], [21], [22].

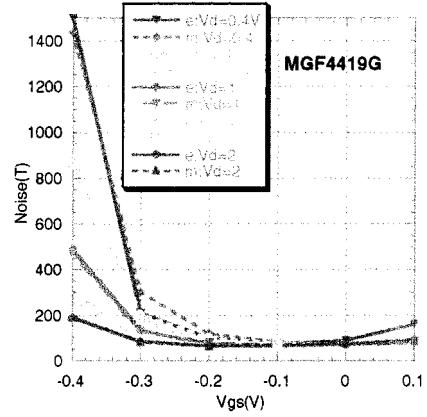

The dc and  $S$  measurements that are required to extract the small- and large-signal equivalent circuit were supplemented with 50- $\Omega$  noise measurements [16] (Fig. 10). The main linear, nonlinear, and noise model parameters were extracted from

Fig. 10. Noise temperature for MGF4419G at 5 GHz.  $G = 50 \Omega$ , 300 K.  $m$ : model.  $e$ : experimental.

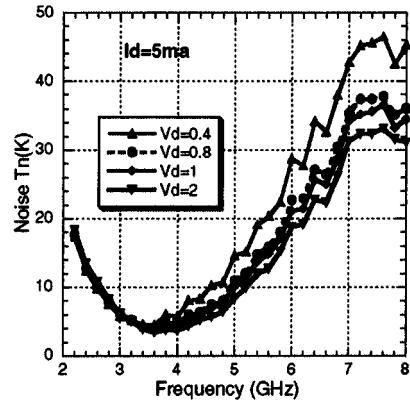

Fig. 11. Noise temperature for MGF4419G at 18 K.  $I_{ds} = 5$  mA.

these measurements. This approach is particularly useful in cryogenic noise model extraction.

In order to precisely evaluate the noise model, a special pre-matched circuit was designed. This is required since the noise temperature, which can be obtained from the high-quality low-noise transistors both at room and at cryogenic temperatures, is very low [2–5 K (see Fig. 11)], which is of the order of the accuracy of a conventional noise measurement system. It is also difficult to use tuners at cryogenic temperatures and, in addition, the designer can face stability problem since high-quality GaAs and InP transistors have very high gain when cooled. The use of the pre-matching circuit solves many of these problems.

Using measured transistor  $S$ -parameters and noise parameters and taking into account the bias networks required to stabilize the transistor at cryogenic temperatures, a simple input matching network is designed for the center frequency of interest. The transistor is bonded into the fixture. The bonding inductance, together with the input matching network, resonates the transistor at the center frequency of the pre-match circuit. In the study, we used GaAs chip transistors MGF4419G and different InP transistors. The gain from the single transistor is typically 10–14 dB, which is why in order to improve the overall accuracy of the noise measurements, a 26-dB room-temperature low-noise amplifier is used to minimize the noise contribution of the system. Both the hot–cold load and cold attenuator method were used for the noise measurements, and the accuracy of the noise measurements is believed to be of the order

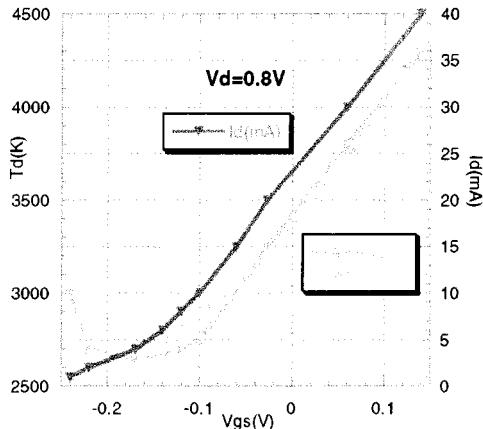

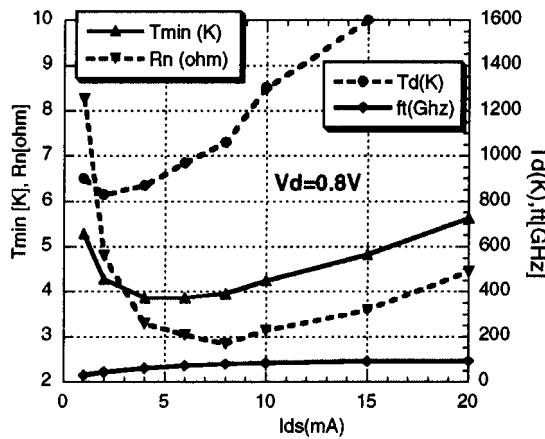

Fig. 12.  $T_d$  versus  $V_{gs}$  for MGF4419G at 18 K.  $V_{ds} = 0.8$  V.Fig. 13.  $T_{\min}$ ,  $R_n$ ,  $T_d$ ,  $F_t$  versus  $I_{ds}$  for MGF4419G at 18 K.

of 1 K. The accuracy of the noise measurements was evaluated by measuring the amplifiers at the Jet Propulsion Laboratory (JPL), Pasadena, CA, the National Radio Astronomy Observatory (NRAO), Charlottesville, VA, and Centro Astronomico de Yebes, Yebes, Spain. All were found to be similar within 1 K.

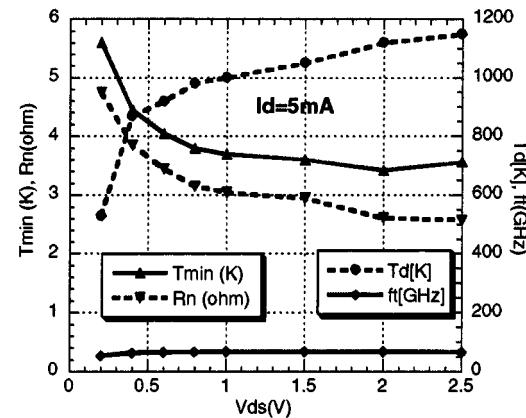

As shown in Figs. 12–14,  $T_d$  follows the  $I_{ds}$  dependence on  $V_{ds}$  and  $V_{gs}$  and, thus, the same type of dependencies as those describing the  $I_{ds}$  can be used to describe the  $T_d$  dependence [3], [7]. This allows us to use the coefficients extracted for the large-signal current model in the  $T_d$  model (Table II) and only fit one more parameter, i.e.,  $t_m$ , for the noise part as follows:

$$T_d = T_{\text{amb}} \left( 1 + t_m \cdot (1 + \tanh(\psi) \tanh(\alpha V_{ds}) (1 + \lambda V_{ds})) \right). \quad (8)$$

At the gate voltage for which the transconductance is at maximum,  $\psi = 0$ , and for  $V_{ds} = 0.6$ –0.7 V, for which  $\tanh(\alpha V_{ds}) \approx 1$  [21],  $f_t$  is maximum.  $T_d$  is then equal to

$$T_d \approx T_{\text{amb}} (1 + t_m). \quad (9)$$

The noise model defined in this way [see (4)–(9)] is, in fact, a large-signal representation of the Pospieszalski noise model. The basic idea in the model [7] is that the channel resistance of the transistors is producing noise as a resistance  $R_{ds}$ , working

Fig. 14.  $T_{\min}$ ,  $R_n$ ,  $T_d$ ,  $F_t$  versus  $V_{ds}$  for MGF4419G at 18 K.

at temperature  $T_d$ , which is higher than the ambient temperature  $T_{\text{amb}}$ . We have

$$R_{ds} = 1/g_{ds} = 1/I_{\text{pk}} (1 + \tanh(\Psi)) (\alpha (1 + \lambda V_{ds}) \cdot \text{sech}(V_{ds})^2 + \lambda V_{ds} \tanh(\alpha V_{ds})). \quad (4a)$$

It has been found from many experimental investigations that the Pospieszalski noise model is very accurate [3], [4], [6], [8], [14], [19], [23] and that there is nearly linear dependence of  $T_d$  versus drain current. Fig. 12 shows measured and modeled  $T_d$  and the fit is good.

In many circuit applications and particularly in the design of cryogenic amplifiers, when good quality transistors biased for low-noise performance are used, the equivalent gate temperature  $T_g$  can be considered equal to the ambient temperature  $T_g = T_{\text{amb}}$ . If a global model is required,  $T_g$  can be modeled using (10) since the main effect of the drain current on  $T_g$  is the heating effect

$$T_g = T_{\text{amb}} \left( 1 + (1 + \tanh(\psi)) \tanh(\alpha \cdot V_{ds}) (1 + \lambda \cdot V_{ds}) \right). \quad (10)$$

For better accuracy, the model can be calibrated at  $I_{ds} = 3 \rightarrow 5$  mA (additional bias points). This means that a global model can be obtained with 2–3 noise measurements. When model parameters are available, it is possible to optimize the amplifier according to the specifications for noise, gain, and power dissipation

$$T_{\min} = 2 \frac{f}{f_t} \sqrt{g_{ds} \cdot T_d \cdot r_{gs} \cdot T_g} \quad (11)$$

$$R_{\text{opt}} \approx \frac{f_t}{f} \sqrt{\frac{r_{gs} T_g}{g_{ds} T_d}}. \quad (12)$$

In some harmonic-balance simulators, the default noise model is the Pucel, Cappy [7]–[10] three-parameter  $P$ ,  $R$ ,  $C$  model. When  $T_d$  and  $T_g$  are available parameters  $P$ ,  $R$ , and  $C$  can be found as

$$R = g_m R_i \frac{T_g}{T_{\text{amb}}} \quad P = \frac{g_{ds}}{g_m} \frac{T_d}{T_{\text{amb}}} + R \quad C = \sqrt{\frac{R}{P}}. \quad (13)$$

This will work well with saturated drain voltages, but when  $V_{ds} = 0$  and  $g_m = 0$ , the singularity in (13) in every large-signal model can cause convergence problem. This can become significant in the analysis of circuits operating at low drain voltages such as resistive, drain mixers, switches, and other circuits operating at low drain voltages. The problem can be solved by adding a small quantity to the denominator that reflects the finite output resistance of the FET or by replacing the function  $1/\tanh$  with

$$\begin{aligned} 1/\tanh |\alpha V_{ds}| &\approx 1/(\tanh |\alpha V_{ds}| + 10^{-7}) \\ &\approx 1 + \alpha^2 / \cosh^2 |\alpha V_{ds}|. \end{aligned} \quad (14)$$

It is convenient to implement the noise models in the simulator using noise current sources. In the MESFET and HEMTs, the main contributor to the noise is the drain current, but, in fact, this noise is higher than the pure Johnson noise generated by  $I_{ds}$ , and this should be accounted for. The total output current contributing to the noise is

$$I_{dtn} = |I_{ds}| + |I_{gd}|. \quad (15)$$

The noise current generators connected at the input and output, as in Fig. 9, are

$$\begin{aligned} I_{dn} &= 4kT(w \cdot 10^{-2}) \sqrt{K_{nd1} I_{dtn} + K_{nd2} I_{dtn}^2} \\ I_{gn} &= 4kT(I_g + I_{dtn}/K_{ng1}) \cdot (2w \cdot 10^{-2}) \end{aligned} \quad (16)$$

where  $K_{ng1}$ ,  $K_{nd1}$  and  $K_{nd2}$  are fitting coefficients and  $w$  is the device size in millimeters. If higher accuracy is required, the correlation between the noise sources can be considered. For GaAs transistor MGF4419G, these coefficients are shown in Table III.

The coefficient  $K_{nd1}$  describes the linear dependence between the drain current and noise, and  $K_{nd2}$  describes the sharp increase of the noise at high drain currents.

The model was implemented as a user-defined model in MDS-HP. As shown in Fig. 10, a high accuracy of the model can be obtained using (16). When it is not necessary to have a global model, the extraction of  $K_{nd2}$  can be omitted. Further, the accuracy of the global model can be improved by using the mixed empirical-table-based approach storing the  $I_{dtn}$  as table data [22].

When all necessary parameters for modeling the transistor are available, it is possible to optimize the amplifier according to our specific requirements concerning noise, gain, power dissipation, etc. Figs. 13, 14, and Table I show typical results for the main noise parameters and their bias dependence, obtained using the pre-matched fixture with MGF4419G. The noise temperature reaches minimum at a drain current  $I_{ds} = 4\text{--}5$  mA. The minimum noise resistance  $R_n$  is lower at higher drain voltages because of the influence of capacitances  $C_{gs}$ ,  $C_{gd}$ . Nevertheless, even at drain voltages  $V_{ds} = 0.5\text{--}0.7$  V, a  $T_{min}$  below 5 K can be achieved with dissipated power of 2–3 mW per transistor. The  $f_t$  does not change much for drain voltages above  $V_{ds} > 0.5$  V and the drain temperature  $T_d$  increase as the drain current and drain voltage increase. By using this information, it is possible to correct the noise models, design the cryogenic amplifier more precisely, and optimize the power dissipation and noise performance. Another issue is selecting the right de-

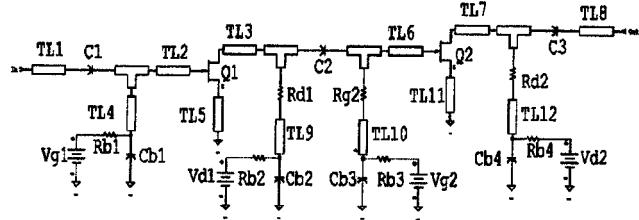

Fig. 15. Two-stage amplifier schematic.

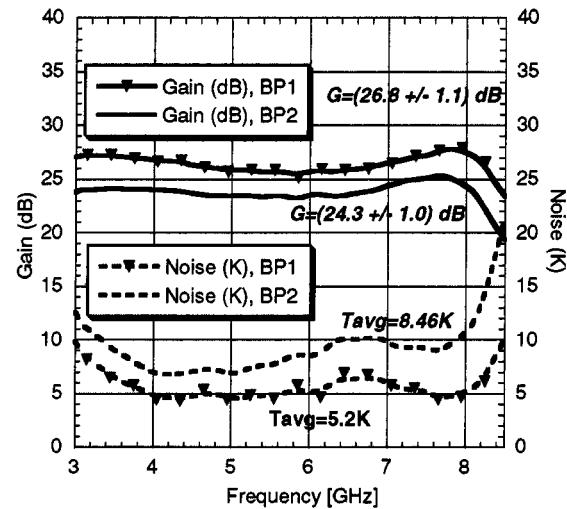

Fig. 16. Gain and noise of the amplifier at 18 K. BP<sub>1</sub> :  $V_{d1} = 2.2$  V,  $V_{d2} = 0.7$  V,  $P_{dc} = 10.5$  mW/stage. BP<sub>2</sub> :  $V_{d1} = 0.7$  V,  $V_{d2} = 0.6$  V,  $P_{dc} = 2.1$  mW/stage.

vice size to obtain optimum input capacitance  $C_{gs}$ , high  $f_t$ , and low  $R_n$ , thus making the matching networks simple in order to achieve broad-band operation [12], [13]. These relations between  $I_{ds}$ , dissipated power, and noise parameters are general for all FETs. It is possible to operate the transistor at drain voltages as low as  $V_{ds} = 0.5\text{--}0.7$  V (and even lower), minimize the power consumption, and still have rather high  $f_t$ , which is one of the key parameters influencing minimum noise [7]. If this approach of combining the large-signal model with the noise model is followed, it is not necessary to make a special bias-dependent noise model, which is difficult and time consuming, especially at cryogenic temperatures. In many circuit simulators, the noise models are already associated with the large-signal models and it is sufficient to calibrate the noise part of the model at a few bias points. Today, procedures for extracting the noise models are well established, and methods used to extract parameters for the Pospieszalski noise model [14] can be used directly for extraction of the noise parameters [see (8), (11), and (12)].

### III. AMPLIFIER DESIGN

The amplifier structure is shown in Fig. 15. In order to improve the input match and stability, and to facilitate noise matching, an inductive source feedback was created by the bond wires. The amplifier performance is shown in Fig. 16. A gain of 22–24 dB and a noise temperature of 7–9.5 K were measured in the frequency range of 4–8 GHz with total power dissipation of 4 mW with commercial transistors. Better results can be achieved using transistors with higher  $f_t$  [6].

#### IV. CONCLUSION

The performance of low-noise transistors was studied at room and cryogenic temperatures with emphasis on minimizing the power consumption and optimizing the amplifier performance. Combining the noise model with the large-signal model can help in the design of low-noise amplifiers with minimum power dissipation. A noise temperature below 9 K and 22-dB gain (two stages) was experimentally obtained with total dc power  $P_{dc} = 4\text{ mW}$  using GaAs transistors. This is close to the best-reported results with InP transistors. The noise model can also be used to design nonlinear circuits like mixers.

#### ACKNOWLEDGMENT

The authors wish to acknowledge Agilent Technologies, Palo Alto, CA, and the Ansoft Corporation, Elmwood Park, NJ, for the donation of high-frequency simulation software, U. Frisk, Swedish Space Corporation (SSC), and G. Florin, SSC, for their strong support of this work. The authors wish to also acknowledge the valuable discussions and help of S. Weinreb, Jet Propulsion Laboratory (JPL), Pasadena, CA, and J. Fernandez, JPL, M. Pospieszalski, National Radio Astronomy Observatory (NRAO), Green Bank, WV, and J. D Gallego, Centro Astronomico de Yebes, Yebes, Spain.

#### REFERENCES

- [1] S. Weinreb, M. Pospieszalski, and R. Norrod, "Cryogenic HEMT low noise receivers for 1.3–43 GHz range," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1988, pp. 945–950.

- [2] M. Pospieszalski, W. Lacatosh, R. Lai, K. Tan, and D. C. Streit, "Millimeter wave cryogenically coolable amplifiers using AlInAs/GaInAs/InP HEMT's," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 515–518.

- [3] M. Pospieszalski, L. Nguen, and M. Lui, "Very low noise and low power operation of cryogenic AlInAs/GaInAs/InP HEMT's," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1994, pp. 1345–1346.

- [4] D. Xu, T. Suemitsu, J. Osaka, and Y. Umeda, "An  $0.03\text{ }\mu\text{m}$  gate length enhancement-mode AlInAs/InGaAs/InP MODFET with 300 GHz FT and  $2\text{ S/mm}$  extrinsic transconductance," *IEEE Electron Devices Lett.*, vol. 5, pp. 206–208, May 1999.

- [5] I. L. Fernandez, J. D. Gallego, and O. Homan, "Low noise cryogenic X-band amplifier using wet-etched hydrogen passivated InP HEMT devices," *IEEE Microwave Guided Wave Lett.*, vol. 9, pp. 413–416, Oct. 1999.

- [6] D. C. Dumka and W. E. Hoke, "Metamorphic InAlAs/InGaAs HEMT's on GaAs substrate with FT over 200 GHz," *Electron. Lett.*, vol. 35, no. 21, pp. 1854–1855, Oct., 14 1999.

- [7] M. Pospieszalski, "Modeling of noise parameters of MESFET's and MODFET'S and their frequency and temperature dependence," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1340–1350, Sept. 1989.

- [8] R. Pucel, H. Haus, and H. Statz, "Signal and noise properties of GaAs microwave FET," in *Advances in Electronics and Electron Physics*. New York: Academic, 1975, vol. 38.

- [9] A. Cappy, "Noise modeling and measurement techniques," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1–10, Jan. 1988.

- [10] A. Cappy and W. Henrich, "High-frequency FET noise performance: A new approach," *IEEE Trans. Electron Devices*, vol. 36, pp. 403–409, Feb. 1989.

- [11] B. Hughes, "A temperature noise model for extrinsic FET's," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 1821–1832, Sept. 1992.

- [12] —, "Designing FET's for broad noise circles," *IEEE Trans. Microwave Theory Tech.*, vol. 41, pp. 190–198, Feb. 1993.

- [13] D. Scherrer, P. Apostolakis, J. Middleton, J. Kruse, and M. Feng, "Optimal noise match of 0.25 micron gate GaAs MESFET's for low power personal communications receiver circuit design," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1994, pp. 1439–1440.

- [14] M. Garcia, J. Stenarson, K. Yhland, H. Zirath, and I. Angelov, "A new extraction method for the two-parameter FET temperature noise model," *IEEE Trans. Microwave Theory Tech.*, vol. 46, p. 1679, Nov. 1998.

- [15] P. Tasker and B. Hughes, "Importance of source and drain resistance to the maximum FT of millimeter-wave MODFETs," *IEEE Electron Device Lett.*, vol. 10, pp. 291–293, July 1989.

- [16] P. Tasker, W. Reinert, B. Hughes, J. Braunstein, and M. Schlechtweg, "Transistor noise extraction using  $50\text{ }\Omega$  measurement system," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 1251–1254.

- [17] B. Klepser, G. Bergamashi, M. Schefer, C. Diskus, W. Patrik, and W. Bächtold, "Analytical bias dependent noise model for InP HEMTs," *IEEE Trans. Electron Devices*, vol. 42, pp. 1882–1888, Nov. 1995.

- [18] R. Reuter, M. Agheten, U. Auer, S. V. Waasen, D. Peters, W. Brockeroff, and F. J. Tegude, "Investigation and modeling of impact ionization with regard to the RF and noise behavior of HFET," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 977–983, June 1997.

- [19] L. Klaproth, A. Schaefer, and G. Boeck, "A bias dependent noise model," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1997, pp. 881–884.

- [20] F. Danneville, G. Dambrine, H. Happy, and A. Cappy, "Influence of the gate leakage current on the noise performance of MESFET's and MODFETs," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 373–376.

- [21] I. Angelov, L. Bengtsson, and M. Garcia, "Extensions of the Chalmers nonlinear HEMT and MESFET model," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 1664–1674, Oct. 1996.

- [22] I. Angelov, N. Rorsman, J. Stenarson, M. Garcia, and H. Zirath, "An empirical table based FET model," *IEEE Trans. Microwave Theory Tech.*, vol. 47, pp. 2350–2357, Dec. 1999.

- [23] I. Angelov, N. Wadeffalk, J. Stenarson, E. Kollberg, P. Starski, and H. Zirath, "On the performance of low DC power consumption cryogenic amplifiers," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, pp. 1237–1240.

**I. Angelov** (M'90) was born in Bulgaria. He received the M.Sc. degree in electronics and Ph.D. degree in physics and mathematics from the Moscow State University Moscow, Russia, in 1969 and 1973, respectively.

From 1969 to 1991, he was with Institute of Electronics, Bulgarian Academy of Sciences, Sofia, Bulgaria, where he was a Researcher, Research Professor (1982), and Head of the Department of Microwave Solid State Devices (1982). Since 1991, he has been with the Chalmers University of Technology, Göteborg, Sweden. His main research interests are device modeling and low-noise and nonlinear circuit design.

**N. Wadeffalk**, photograph and biography not available at time of publication.

**Jörgen Stenarson** (S'98) received the M.Sc. degree in engineering physics from the Chalmers University of Technology, Göteborg, Sweden, in 1997, and is currently working toward the Ph.D. degree in microwave electronics at the Chalmers University of Technology.

His research interests are noncontacting *S*-parameter measurements, FET noise models, noise model extraction methods, and low-noise amplifier design.

**Erik Ludvig Kollberg** (M'83–SM'83–F'91) is currently a Professor with the School of Electrical and Computer Engineering, Chalmers University of Technology, Göteborg, Sweden, where he has been since 1980. He was an Invited Guest Professor at the Ecole Normal Supérieure, Paris, France, and a Distinguished Fairchild Scholar at the California Institute of Technology, Pasadena, in 1990. His research has comprised low-noise millimeter-wave Schottky diode mixers, varactor diode multipliers, superconducting quasi-particle (SIS) mixers, quantum-well devices, submillimeter-wave hot electron mixers, and three-terminal devices such as FETs and heterojunction bipolar transistors (HBTs). He invented the heterostructure barrier varactor diode. In the fields above-mentioned, he has authored or co-authored approximately 250 scientific papers.

Dr. Kollberg is a member of the Royal Swedish Academy of Science and the Royal Swedish Academy of Engineering Sciences. He was the recipient of the Microwave Prize presented at the 12th European Microwave Conference, Helsinki, Finland and the 1986 Gustaf Dahlén Gold Medal. He was also the recipient of an Honorary Ph.D. degree presented by the Technical University of Helsinki, Helsinki, Finland, in 2000.

**Piotr Starski** (S'76–M'78–SM'92) was born in Lodz, Poland, in 1947. He received the M.S. and Ph.D. degrees in electrical engineering from the Chalmers University of Technology, Göteborg, Sweden, in 1973 and 1978 respectively.

In 1983, he became an Associate Professor with the Chalmers University of Technology. From 1972 to 1978, he was with the Division of Network Theory, Chalmers University of Technology. From 1978 to 1979, he was a Design Engineer at Anaren Microwave Inc., Syracuse, NY. From 1979 to 1997, he was a Researcher with the Division of Network Theory and Division of Microwave Technology, Chalmers University of Technology. He is currently a Docent with the Microwave Electronics Laboratory, Chalmers University of Technology. His current research activities are in the area of microwave circuits and devices as well as in interconnections for RF applications.

Dr. Starski was chairman of the IEEE Sweden Section from 1987 to 1992 and vice-chairman from 1992 to 1999. He was the recipient of a 1978 Fellowship of the Sweden–America Foundation.

**Herbert Zirath** (S'84–M'86) became an Associate Professor with the Department of Microwave Technology, Chalmers University of Technology, Göteborg, Sweden, in 1992, and Professor in 1996. He currently leads a group of approximately 20 people, including six senior researchers and eight Ph.D. students. This group is involved with fabrication, design, and characterization of InP-HEMT devices and circuits, SiC and GaN MESFETs for high-power applications, device modeling including noise and large-signal models for FET and bipolar devices, and foundry related monolithic microwave integrated circuits (MMICs) for millimeter-wave applications. He is also with Microwave System AB, Ericsson, Mölndal, Sweden